AMD今天发布了7纳米的Instinct MI100 GPU,同时还发布了一系列来自戴尔、惠普和Supermicro的设计成果。MI100标志着AMD专注于计算的CDNA GPU架构的第一次迭代。新架构提供高达11.5 TFLOPS的FP64峰值吞吐量,使Instinct MI100成为FP64中第一个突破10 TFLOPS的GPU,比上一代MI50提高了3倍。它在FP32工作负载中拥有23.1 TFLOPS的峰值吞吐量,在这两个类别中都击败了英伟达的糟糕的A100 GPU,尽管它在其他数字格式中滞后。

正如人们对数据中心GPU的预期,PCIe 4.0卡是为AI和HPC工作负载而设计的,还支持AMD的第二代Infinity Fabric,使卡之间的点对点(P2P) I/O带宽翻倍。这种结构允许卡与CPU共享一个统一的内存地址空间,这对AMD来说是一个关键优势,因为它充分利用了其作为目前唯一提供数据中心级gpu的CPU供应商的地位。这些卡在三个Infinity Fabric链路上拥有高达340 GB/s的总吞吐量,并被设计成部署到四核蜂巢(每个服务器最多两个),每个蜂巢支持高达552 GB/s的P2P I/O带宽。

本能MI100还支持AMD的新矩阵核心技术,提高单精度和混合精度矩阵操作的性能,如FP32, FP16, bFloat 16, INT8和INT4。该技术将FP32的性能提升至46.1 TFLOPS。

这些存储卡配有32GB的HBM2内存,分布在四个堆栈上,提供总计高达1.23 TB/s的带宽。AMD声称,与英伟达的A100 gpu相比,这款显卡的峰值性能每美元可提高1.8到2.1倍。

AMD公司还宣布,其开源的ROCm 4.0开发软件现在拥有的OpenMP 5.0,HIP,PyTorch和Tensorflow一个开源编译器和统一的支持。

该卡具有300W的TDP,并采用标准的PCIe插件卡(AIC)形式,带有两个8针电源连接器。考虑到数据中心的重点,卡缺乏显示输出,而被动冷却卡有一个大网格的后I/O屏蔽,以有效的气流。

| 峰时钟 | 流处理器 | 计划书 | HBM2记忆 | 内存带宽 | PCIE接口 | |

| 7纳米本能MI100 | 1502兆赫 | 7680(120 CU) | 300 w | 32 gb | 1.23 TB /秒 | 4.0 |

| 7纳米本能MI50 | 1725兆赫 | 3840(60铜) | 300 w | 32 gb | 1.024 TB /秒 | 4.0 |

| 7nm Nvidia A100 (PCIe) | 1410兆赫 | 6912 | 250 w | 40GB. | 1.555 TB /秒 | 4.0 |

| 7nm Nvidia A1000 (HGX) | 1410兆赫 | 6912 | 400 w | 40GB. | 1.555 TB /秒 | 4.0 |

AMD将MI100的峰值时钟频率从上一代MI50的1725 MHz降至1502 MHz,但将计算单元数量增加了一倍,达到120台。该公司还将内存带宽提高到1.23 TB/s。

| FP64 | FP32 | 矩阵FP32 | 矩阵FP16 | INT4 / INT8 | bFloat16 | |

| 7纳米本能MI100 | 11.5 TFLOPs | 23.1 TFLOPS | 46.1 TFLOPS | 184.6万亿次 | 184.6 | 92.3 |

| 7纳米本能MI50 | 6.6 TFLOPS | 13.3 TFLOPS | 13.3 TFLOPS | 26.5 TFLOPS | - | - |

| 7nm Nvidia A100 (PCIe) | 9.7 TFLOPS | 19.5 TFLOPS | 156 TFLOPS(张量) | 312年TFLOPS | 624 / 1248(张量核心) | 624 / 1248(张量核心) |

| 7nm Nvidia A1000 (HGX) | 9.7 TFLOPS | 19.5 TFLOPS | 156 TFLOPS(张量) | 312年TFLOPS | 1248(张量的核心) | 1248(张量的核心) |

的改进,向CDNA架构(我们将在下面介绍)的净效应提供了一个1.74X的增益峰值FP64和FP32吞吐量,高达3.46X改善矩阵FP32和6.97X的增益矩阵FP16。这些收益来AMD的新的Matrix核心技术的礼貌与混合数据类型优化的新基质芯引擎增强的CU。

AMD的MI100击败了Nvidia A100峰值FP64和FP32吞吐量〜15%,但在矩阵FP32,FP16和INT4 / INT8和bFloat16工作量Nvidia的A100仍然提供了远远优于吞吐量。

AMD称MI100可以与6兆瓦的ASCI White竞争,后者是2000年世界上速度最快的超级计算机,重达106吨,性能为12.3 TFLOPS。相比之下,MI1000将功率降至300W,重量仅为2.56磅,性能为11.5 TFLOPS。

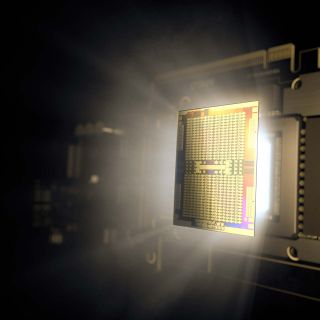

AMD本能MI100 CDNA架构

AMD分拆其图形架构到RDNA平台的计算负载图形重点工作(游戏)和cDNA(HPC / AI负载),因此它可以提供有针对性的改进每个相应的架构。自然地,该装置的设计CDNA来没有许多所需图形的工作,如光栅化,镶嵌,图形缓存,混合和显示引擎传统的固定的功能块。该CDNA架构确实保留HEVC,H.264和VP9解码一些逻辑,这是机器学习的工作负载重要的焦点上的物体检测。

7nm的Instinct MI100标志着CDNA架构的第一次迭代,并带有PCIe 4.0接口,支持16gt /s连接到CPU (32gb /s双向)。AMD并没有分享7纳米芯片的尺寸,也没有分享晶体管的数量,但我们知道120个增强CUs被分成4个计算引擎。每个CU都有一个矩阵核心引擎,可以提高各种数字格式的计算吞吐量,AMD将其描述为:

“经典GCN计算核心含有多种用于标量和向量指令优化管道等。特别地,每个CU包含一个标量寄存器文件,标量执行单元,和一个标量数据高速缓存来处理指令,其跨越所述波前共享,例如作为共同的控制逻辑或地址运算。类似地,CU的也包含四个大向量寄存器文件,它们为FP32优化4个向量执行单元,和一个矢量数据的高速缓存,通常,载体管道是16宽,并且每个64宽波阵面在四个周期中执行“。

AMD的CDNA架构建立在GCN的标量和矢量基础上,并添加矩阵作为一级公民,同时增加了对机器学习的新数字格式的支持,并保留了为GCN架构编写的任何软件的向后兼容性。这些矩阵核心引擎增加了一个新的波前级指令家族,矩阵融合乘加或MFMA。MFMA家族使用四种不同类型的输入数据:8位整数(INT8)、16位半精度FP (FP16)、16位脑FP (bf16)和32位单精度(FP32),执行混合精度算术并对KxN矩阵进行操作。所有MFMA指令要么产生32位整数(INT32),要么产生FP32输出,这减少了矩阵乘法最后积累阶段溢出的可能性。”

矩阵执行单元处理MFMA指令并减少寄存器文件读取的数量,因为许多矩阵乘法输入值被重用。

共享8MB的L2高速缓存在物理上分割为32片(两次多达MI50)和是16路组相联。总体而言,32片提供高达6TB / s的总吞吐量。存储器控制器支持ECC HBM2的4或8高堆垛在2.4 GT /秒,具有1.23 TB的集合体理论吞吐量/秒。这比前根型号快20%。

AMD第二代Infinity Fabric

AMD的cpu到gpu的Infinity Fabric已经被证明是一个关键的进步,帮助公司赢得了许多百亿亿次级合同。该技术支持cpu和gpu之间的共享内存/缓存一致性,通过减少系统内的数据移动量来减少延迟、提高性能并降低功耗。

第二根无限面料链接在23 GT操作/秒和16位宽的,就像以前的根,但最新的版本支持第三连接,使四GPU配置。这种新的设计最适合在四GPU荨麻疹,具有典型的双插槽服务器支持两个蜂箱 - 每个CPU之一。

这些蜂箱在全连接的拓扑结构中运行,而之前的加速器使用的是环形拓扑结构。新的拓扑在所有的减少和分散/聚集操作中提高了性能。

总的来说,AMD的第二代Infinity Fabric提供了两倍的点对点(P2P) I/O带宽,每张卡(有三个链路)增加了两个340 GB/s的吞吐量。一个四gpu的蜂箱提供了高达552 GB/s的P2P I/OP吞吐量,表明这种结构不是线性伸缩的。

完全连接的拓扑结构和共享地址空间是AMD相对于Nvidia的关键优势并导致几个显着的exascale超级合同。值得注意的是,Nvidia公司尚未公布的百亿亿次超级计算机的合同,但AMD的加速器已经开始享受超级计算和高性能计算领域广泛的摄取。

AMD还宣布,到今年年底,Dell、Gigabyte、HPE和联想等主要OEM厂商将提供搭载Instinct MI100的完全合格OEM系统。